Efficient debugging workflow in chip circuit verification - A targeted simulation approach

Chip circuit verification is a vital to the

semiconductor industry, ensuring that integrated circuits meet design

specifications and quality standards.

By Slava Zhuchenya, Product Engineer supporting

Calibre interface tools in the Design-to-Silicon division of Siemens Digital Industries Software

During the verification process, engineers aim to identify and resolve potential design flaws or violations before the chip goes into production. To meet tight tape-out deadlines, verification simulations need to be as fast as possible, as there can be many iterations of these runs.

However, that is only part of the challenge. IC designers need to quickly identify circuit issues, but fixing them requires debug data. Traditional approaches either sacrifice speed by including all debug data in the main verification run or compromise debug capabilities by omitting crucial data to expedite the process. Balancing the need for fast verification with the necessity of detailed debug information presents a dilemma.

Chip circuit verification is a vital to the semiconductor industry, ensuring that integrated circuits meet design specifications and quality standards. During the verification process, engineers aim to identify and resolve potential design flaws or violations before the chip goes into production. To meet tight tape-out deadlines, verification simulations need to be as fast as possible, as there can be many iterations of these runs.

However, that is only part of the challenge. IC designers need to quickly identify circuit issues, but fixing them requires debug data. Traditional approaches either sacrifice speed by including all debug data in the main verification run or compromise debug capabilities by omitting crucial data to expedite the process. Balancing the need for fast verification with the necessity of detailed debug information presents a dilemma.

Challenges to debugging workflows in IC verification

In chip circuit verification, there is often a trade-off between the speed of verification runs and the availability of helpful data to fix the violations. Running a full verification job with all the useful debug data can be time and resource-consuming and lead to an explosion of data volume. The more information there is to process and write to disk, the more it will cost.

Conversely, excluding key data to accelerate verification iterations may hinder the ability to effectively debug results later.

The time savings in one stage may become a penalty in a later stage. The challenge lies in finding a middle ground that allows for fast verification while enabling efficient debugging without compromising either, as both of these are a crucial part of chip design and verification.

A solution for balancing verification speed with detailed debug

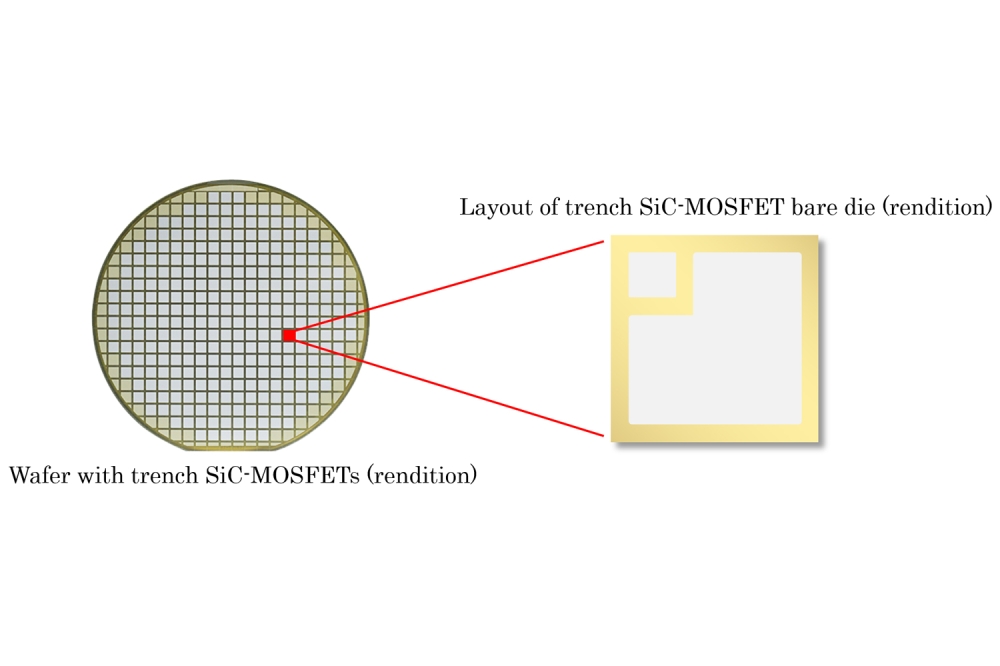

Figure 1. A targeted debug-focused simulation integrated into the debugging stage.

A better solution involves integrating targeted debug-focused simulations into the debugging stage itself instead of an all-or-nothing approach (figure 1).

Not every result needs detailed debug data. At least not right away. Some results might be waived later or could be fixed as a result of fixing some larger underlying problems that can eliminate many violations. Instead of choosing between running a full verification job fast or running it with all the necessary debug data, why not give users the ability to decide later when their needs become clearer?

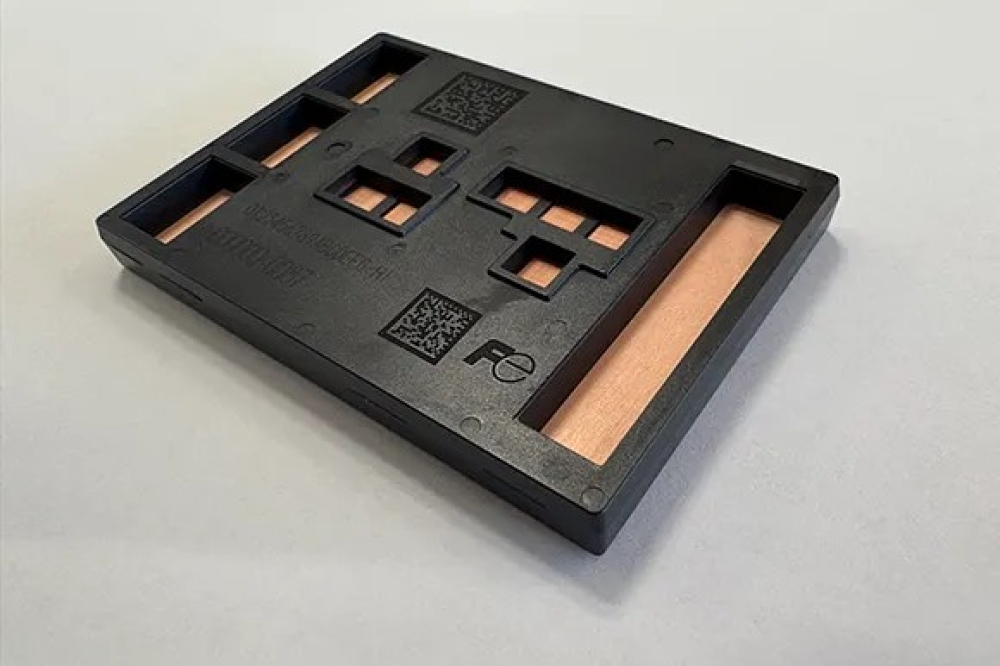

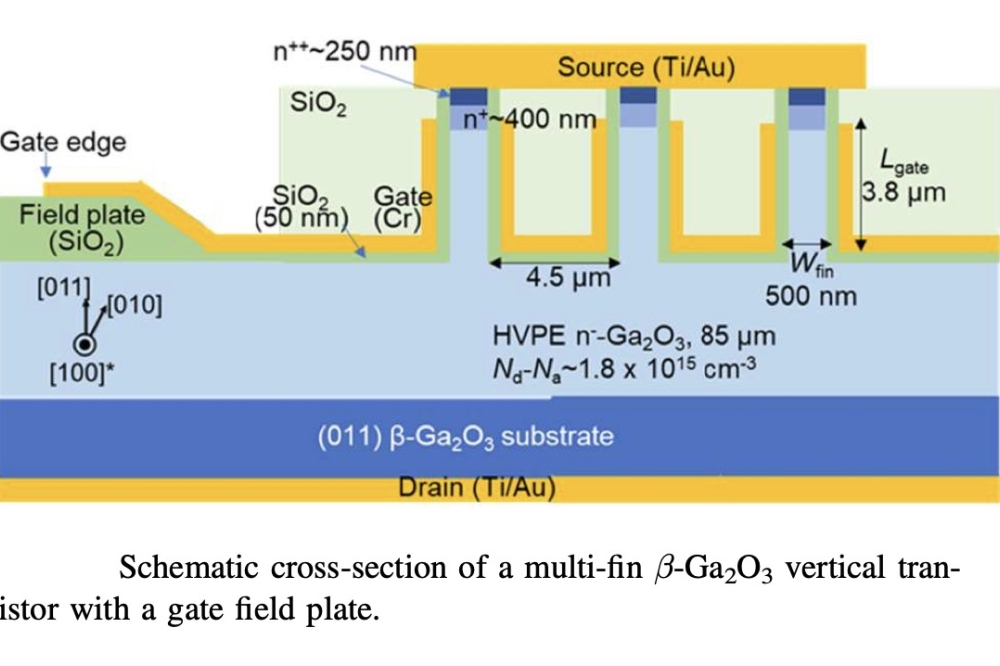

Figure 2. Calibre RVE debug environment offers the data needed for debug.

A designer first wants to see what rule violations they have in their simplest form and then decide how they need to act for each result. This approach allows designers to obtain debug data for specific results right from within the debug environment (figure 2).

Once it is clear that more information is needed, the debug tool should let the user run smaller targeted data-rich simulations just on the interesting results. This way, the full verification remains fast, and getting debug data is achievable without the overhead of a massive verification job.

Calibre PERC point-to-point example

Calibre PERC’s point-to-point (P2P) simulation is a circuit reliability verification solution that checks for the presence and impact of parasitic resistance in an IC layout. Parasitic resistance in chip design refers to the unintentional resistance that arises due to the physical layout and interconnections of the components on the chip.

This resistance can have a significant impact on circuit performance and reliability when it is manufactured. Calibre PERC P2P simulations calculate the total effective parasitic resistance between two or more points in the

IC layout, to check if the resistance does not exceed allowable thresholds that ensure a chip will work as designed.

These simulations can be complex and time-consuming to run but are a crucial for circuit reliability. As with most IC verification flows, simulation runtime is key to successful and timely chip tape-outs. In particular, the more iterations that are required, the more the full verification runtime starts to impact the tape-out schedule. For this reason, P2P simulations report minimal information on the violations, like the effective resistance value and the nets involved. In some cases, a designer might know the layout well enough, and a violation could be simple enough that the fix could be obvious. However, more often than not, additional debug data is needed to fully understand the source of the violation.

Debugging point-to-point violations requires analyzing chip layout interconnect and determining what routing practices might be causing a higher-than-expected or allowed total resistance value. Doing this with only the net and the effective resistance between some points on the layout can be a significant challenge.

Designers may need more information to determine what part of the net layout is contributing the most to the high parasitic resistance. Making guesses and then rerunning the verification simulation can quickly become very expensive.

Detailed data about the interconnect polygons reveals what is happening between the points and can save time by limiting the number of verification reruns that need to happen. Resistance contribution and current density data for individual layout polygons give designers the data they need to better debug these results. However, including all that polygon data for every violation would then significantly increase runtime and database sizes for those runs. How do you find a good middle-ground approach?

Calibre RVE PERC now allows designers to run Calibre PERC P2P Debug simulations on select P2P results directly from the debug GUI. This means that designers can get debug data for specific P2P results on demand without leaving the debug environment. They can run the full PERC P2P flow on their design without needing to make any predictions on what debug data they’ll need. Once it is clear that more information is needed, RVE lets you run smaller targeted P2P simulations that gather the polygon data just for interesting results (figure 3).

Figure 3. Run Calibre PERC P2P Debug simulations on select P2P results directly from the debug GUI.

The added database contains information like current density, resistance calculations, and percentage of resistance contribution of the individual polygon. This data significantly increases designers’ productivity during the debug process without compromising the runtime of the full Calibre PERC P2P simulation.

The improved workflow begins with the standard execution of the main P2P verification run, optimized for speed by excluding non-essential debug data. Upon identifying potential violations in the results, engineers transition to the debug environment and stay there even if they need to make additional runs to extract more debug data for select violations. This is a much more efficient, productive and intuitive flow.

Conclusion

Efficient debugging in chip circuit verification requires a balanced approach that optimizes verification speed without compromising debug capabilities. By integrating targeted simulations into the debugging environment itself, engineers can obtain additional debug data selectively and iteratively, minimizing the need for full verification reruns and setup efforts. This approach maximizes productivity and accelerates time-to-market while ensuring the reliability and functionality of integrated circuits.

Calibre PERC P2P is one such circuit verification simulation that benefits from this improved debug flow. Calibre RVE PERC streamlines the debug process by enabling targeted P2P simulations within the debug environment, providing detailed debug data without compromising full verification runtime, significantly boosting productivity for designers.